## Considerations for Embedding Passives and Actives in PCBs

**PwrSoC 2014**

AT & S Austria Technologie & Systemtechnik Aktiengesellschaft | Fabriksgasse 13 | A-8700 Leoben Tel +43 (0) 3842 200-0 | E-mail info@ats.net

www.ats.net

### Agenda

Why embedding?

**Embedding flavours**

**Embedding by AT&S**

**Reliability comparison**

Supply chain

Comparison with QFN

Conclusion

#### Styles

- Layer embedding

- → Capacitive and/or resistive layers

- Partial embedding

- → Cavities in substrates

- Full embedding

- → Components in substrates

- ➡ Focus on ECP from AT&S

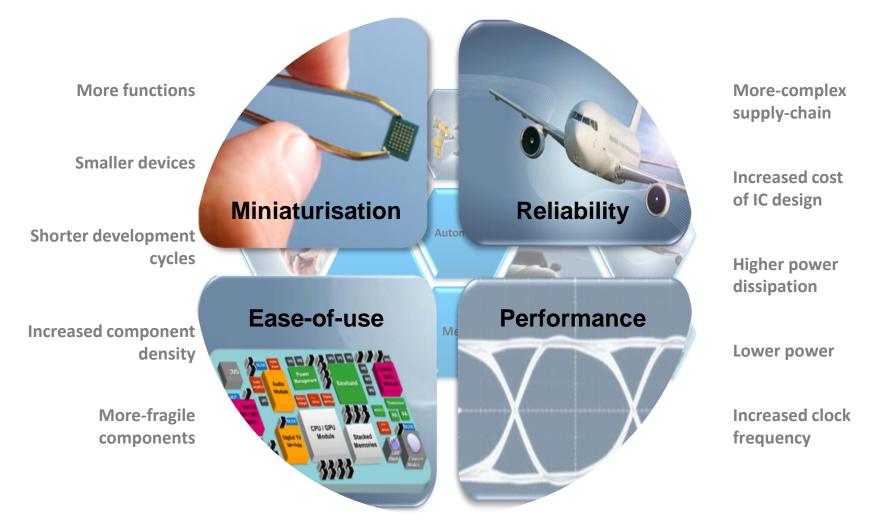

### Why are we embedding?

#### Trends and challenges in electronics

### Agenda

#### Why embedding?

**Embedding flavours**

**Embedding by AT&S**

**Reliability comparison**

Supply chain

Comparison with QFN

Conclusion

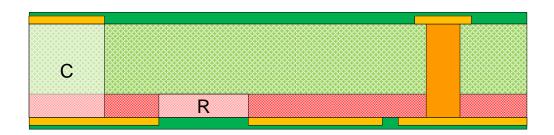

#### Embedded layer

- Pros

- High flexibility in number and position of passive functions

- General compatibility with standard PCB processes

#### Cons

- Higher material cost than standard PCB

- Limitation to low passive values

- Limitation to passive functions

### **Embedding flavours**

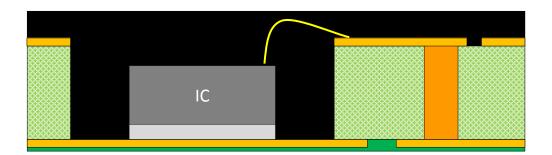

#### Partial embedding

- Pros

- Similar price to standard PCB

- Compatibility with standard components

- Possibility to improve electrical/thermal performance

- Cons

- Increased complexity of component placement

- Loss of integration

- Limitation to wirebonded actives for low-layer-count PCBs

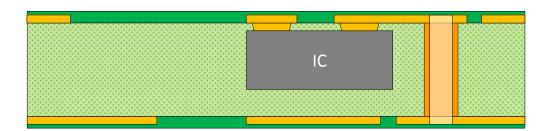

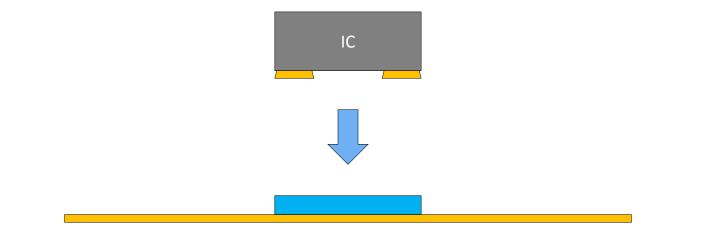

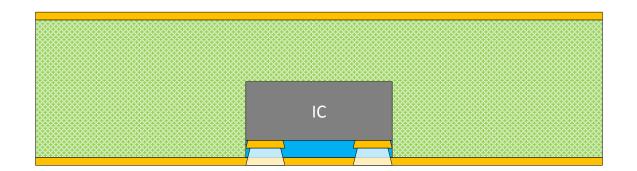

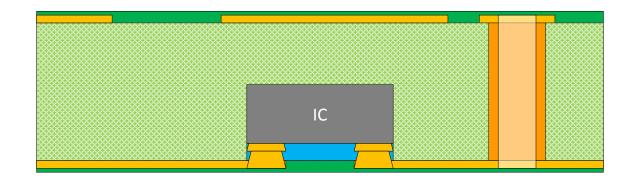

#### Full embedding

#### Pros

- Miniaturisation through 3D integration

- Increased performance through short connections

- Increased performance through heat conduction

- Cons

- Higher m2 price

- Limitation to process-compatible components

### Agenda

Why embedding?

**Embedding flavours**

**Embedding by AT&S**

**Reliability comparison**

Supply chain

Comparison with QFN

Conclusion

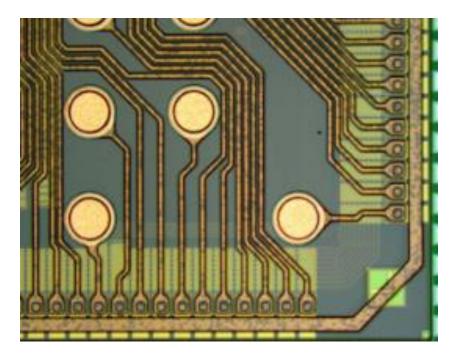

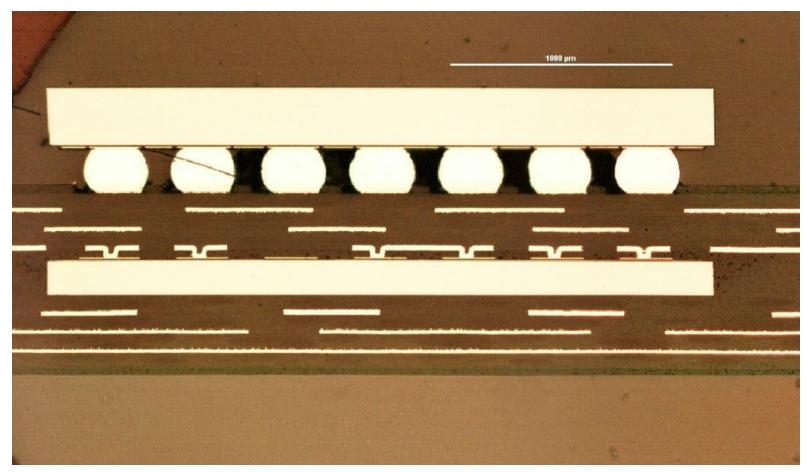

**Component placement**

#### **Component placement**

1 ASM X4 equivalent to 80 die placers

| 5. COM 5. COM 5. COM 5. COM |

|-----------------------------|

PCB and interconnect formation

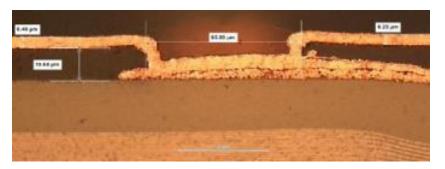

#### Interconnect formation

1 laser-drilling station equivalent to 100 wirebonders

Structuring and finish

#### Requirements

- Cu terminations (minimum 5 mm)

- Components in tape-&-reel

- Nothing else!

#### Benefits

- High integration

- High performance

- Very-high-scale production

- ⇒ Efficient and cost-effective technology

### Agenda

Why embedding?

**Embedding flavours**

**Embedding by AT&S**

**Reliability comparison**

Supply chain

Comparison with QFN

Conclusion

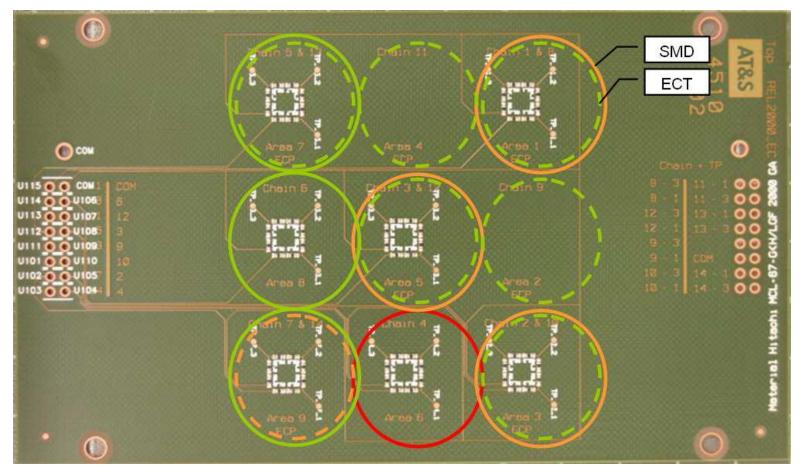

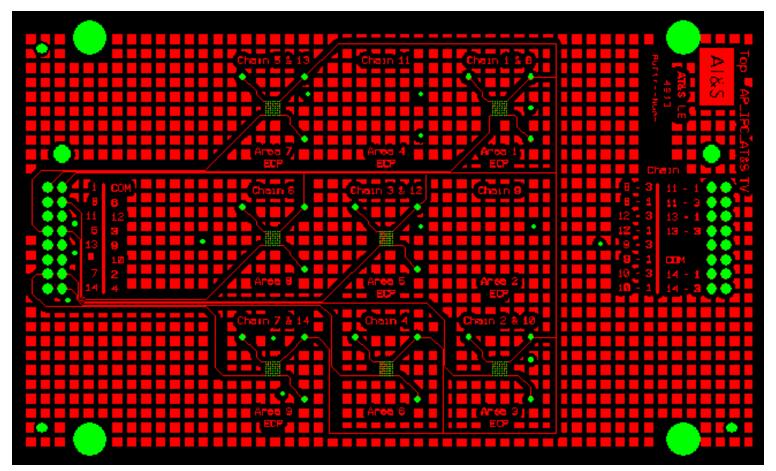

### AT&S

- Drop test (JESD22-B111) @ 1500 g

- SMT components (126 daisy chains)

- ⇒ First failure @ 304 drops

- → 100-% failure @ 974 drops

- ECP components (126 daisy chains)

- ⇒ First and only failure @ 832 drops

- → Test end @ 1000 drops

- TCT (JESD22-A104C) @ [-40; +125] degC

- SMT components (35 daisy chains)

- → Zero failure @ 1000 cycles

- ECP components (35 daisy chains)

- → Zero failure @ 1000 cycles

### AT&S

- Drop test (JESD22-B111) @ 1500 g

- SMT components (70 daisy chains)

- ⇒ First failure @ 792 drops

- → 4 failures @ 1000 drops

- ECP components (70 daisy chains)

- → Zero failure @ 1000 drops

- TCT (JESD22-A104C) @ [-40; +125] degC

- SMT components (70 daisy chains)

- ⇒ First failure @ 684 cycles

- ⇒ 100-% failure @ 999 cycles

- ECP components (70 daisy chains)

- ⇒ Zero failure @ 1000 cycles

- Bend test (JEDEC-9702) @ 2 mm/min (28 mm maximum)

- SMT components (63 daisy chains)

- ⇒ First and only failure @ 3.71 s

- ECP components (63 daisy chains)

- → Zero failure @ 14 min

### Agenda

Why embedding?

**Embedding flavours**

**Embedding by AT&S**

**Reliability comparison**

Supply chain

Comparison with QFN

Conclusion

### AT&S

#### **Suppliers**

#### Actives

- Cu available from selected foundries

- RDL available from OSATs

- Passives

- Resistors available from AVX and Murata

- Capacitors available from KOA and Panasonic

#### IPDs

- Available from IPDiA , Maxim and STMicroelectronics

#### Technology complexity (or lack thereof)

- Standard PCB processes

- Standard SMT processes

- Main production facilities in China

- → Very quick capacity extension possible

#### Integration in packaging flow

- Very-high-yield process

- ⇒ 2L @ 99+ %

- Flexibility of delivery format

- → Any size up to 400\*550 mm

- Intermediate-testing relevance

- If QFN replacement

- → Only after singulation

- If SiP

- → Do you test after every component placement/interconnection?

- → Seamless integration in standard packaging flow

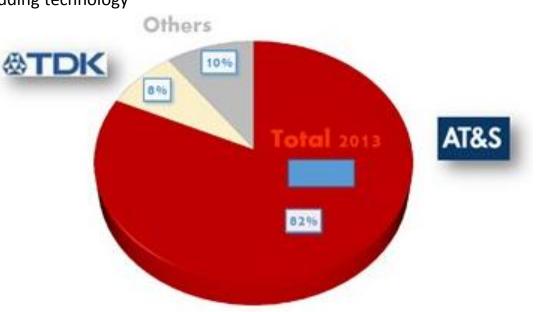

#### Partnership

- Agreement with TDK-EPCOS

- TDK-EPCOS as second source for ECP

- AT&S as second source for SESUB

- → Limiting customer concerns with regards to technology selection/dissemination

- Co-development of next-generation embedding technology

- Need to encourage ecosystem

- → Risk of customer distrust (monopoly)

### Agenda

Why embedding?

**Embedding flavours**

**Embedding by AT&S**

**Reliability comparison**

Supply chain

**Comparison with QFN**

Conclusion

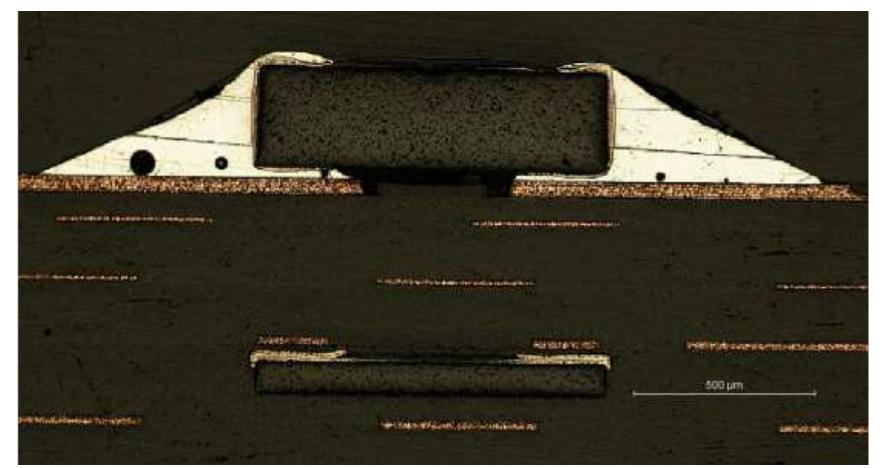

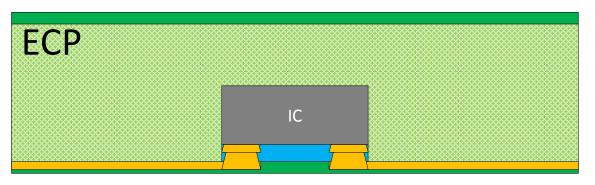

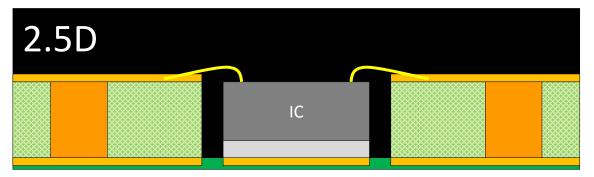

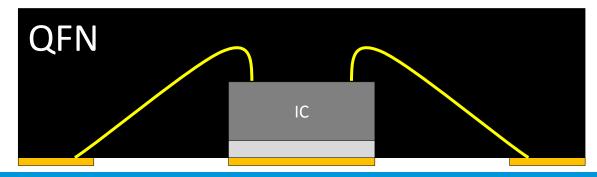

### **Comparison with QFN**

#### Structure

#### Characteristics

|                              |                      | ECP           | 2.5D | QFN |

|------------------------------|----------------------|---------------|------|-----|

| Die size (mm)                |                      | 2*2           |      |     |

| Package size (mm)            |                      | 4*4           |      |     |

| Number of I/Os               |                      | 12            |      |     |

| Die thickness (µm)           |                      | 150           | 300  | 300 |

| Package thickness            |                      | 300           | 500  | 700 |

| Interconnect                 |                      | Via           | WB   | WB  |

| Thermal resistance (K/W)     | $\theta_{j-top}$     | 30            | 94   | 120 |

|                              | $\theta_{j-bottom}$  | 0.7           | 0.6  | 0.7 |

|                              | $\theta_{j-ambient}$ | 0.7           | 0.6  | 0.7 |

| Interconnect inductance (nH) |                      | 0.7           | 0.7  | 1.0 |

| Cost                         |                      | +             | +    | 0   |

| Testability                  |                      | QFN footprint |      |     |

### Agenda

Why embedding?

**Embedding flavours**

**Embedding by AT&S**

**Reliability comparison**

Supply chain

Comparison with QFN

Conclusion

### Conclusion

#### Embedding

- Different variants depending on requirements

- Embedded layer

- Partial embedding

- Full embedding

- Improved performance for limited to neutral cost increase

- Size reduction

- Improved thermal resistance

- Improved electrical characteristics

- Maturing and reliable technology

- Full supply chain in place with second-source options

- ⇒ What will be the next big application?

# Thank you for your attention!

# **Questions?**

AT & S Austria Technologie & Systemtechnik Aktiengesellschaft | Fabriksgasse 13 | A-8700 Leoben Tel +43 (0) 3842 200-0 | E-mail info@ats.net

www.ats.net